Question 16.7: What is the difference between programmable logic array (PLA......

What is the difference between programmable logic array (PLA) and programmable array logic (PAL)? Explain PAL in detail.

Learn more on how do we answer questions.

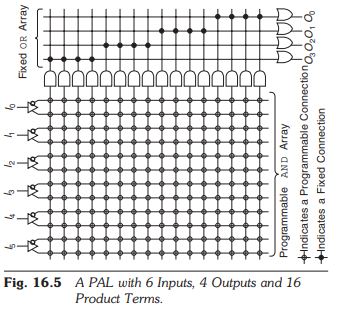

PLA is costly when the number of functions to be realized is low. In such cases, we make use of programma- ble array logic (PAL) chips. A PAL chip is a special modification of programmable logic array (PLA) chips. In a PAL, the AND array is programmable as in the case of PAL, but the OR array is fixed i.e. the AND array contains fusible links and hence can be programmed, but the OR array connections are fixed and contain no fusible links, hence the OR array is not programmable. Figure 16.5 shows the structure of a PAL. We make use of the same symbol in the structure of PAL as we have done for PLA.

PALs are much cheaper than PLAs, hence many logic designers prefer PALs as compared to PLAs. The advantages of PLAs come into effect only when all of its individual OR gates are used in the logic design. In many situations this may not be required. In such cases, using PALs will be more economical.

PAL manufactures compensate for the absence of a programmable OR array by providing a range of devices with different numbers of OR gates and with different numbers of inputs on each OR gate.

Because the OR array is fixed in a PAL it is common to omit this array from its symbolic representation. It is also common to move the inputs to the left of the diagram to produce or circuit with the inputs on the left and output on the right, as shown in Fig. 16.6.